KFLOP - RS232

KFLOP содержит UART, который позволяет C программам пользователя выполнять последовательную связь с другими сторонними устройствами.

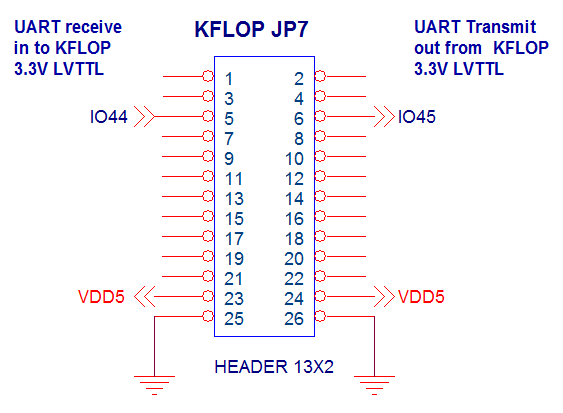

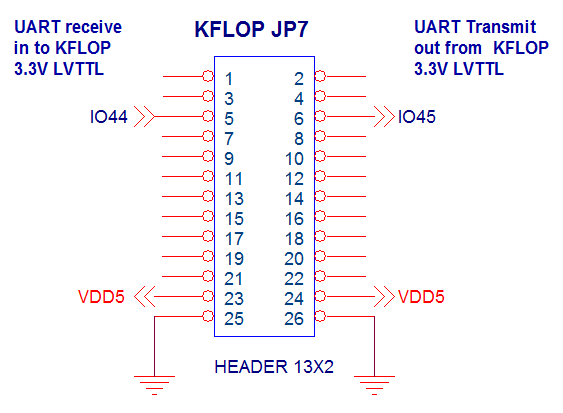

KFLOP содержит последовательный интерфейс UART, но не имеет схемы для согласования сигналов при уровнях напряжения +3 ... 25 В ... -3 ... -25 В, заданных стандартом RS232. Сигналы передачи и приема KFLOP являются логическими сигналами LVTTL 3,3 В.

Обратите внимание: сигналы, поступающие непосредственно от KFLOP, не совместимы с RS232. Подключение KFLOP напрямую к RS232 может привести плату к выходу из строя.

Плата Kanalog имеет преобразователь LVTTL(см. ниже).

KFLOP + Kanalog - RS232

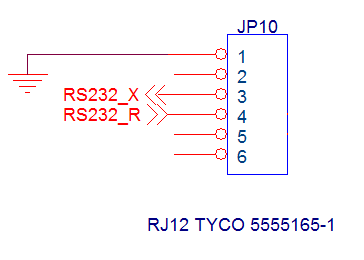

Kanalog содержит преобразователь логических уровней KFLOP UART в стандартные уровни напряжения RS232. Сигналы RS232 доступны в JP10, который является стандартным разъемом RJ12.

Распиновка показана ниже. Распиновка рассчитана на совместимость с некоторыми устройствами ПЛК. Обратите внимание, что 6-жильный кабель должен быть заземлен через вывод 1.

KFLOP UART Software

FPGA KFLOP реализует программируемую скорость UART с двойной буферизацией 1 символа при передаче и приеме. Для использования UART необходимо использовать С программу пользователя KFLOP. Необходимо задать параметры для управления каким-либо конкретным устройством.

Программы пользователя KFlop с 1 активным потоком выполняются каждые 180US. (См. здесь для получения дополнительной информации). Это позволяет достичь скорости до 38400 бод без потерь данных (10 бит при 38400 Гц = 260 мкс). Передаваемые и принимаемые данные содержат 8 бит. Если требуется проверка четности, она должна обрабатываться программой пользователя.

Чтобы установить скорость передачи в бодах, введите 8-разрядный делитель скорости в регистр FPGA (RS232_BAUD_REG)

Для передачи 8-битовый символ записывается в регистр FPGA (RS232_DATA).

Чтобы получить символ, прочитайте 8-битное значение из регистра FPGA (RS232_DATA)

Регистр состояния (RS232_STATUS) предоставляет 2 бита статуса, которые можно использовать для определения, принят ли символ (RS232_DATA_READY), и есть ли возможность передать символ (RS232_TRANSMIT_FULL)

Следующие определения были добавлены в файл KMotionDef.h.

//RS232 FPGA Register Definitions

#define RS232_STATUS 0xc1 // Status Reg Address

#define RS232_DATA 0xc0 // 8 bit data read/write reg address

#define RS232_DATA_READY 0x01 // Data ready to read status mask

#define RS232_TRANSMIT_FULL 0x02// Transmit buffer full status mask

#define RS232_BAUD_REG 0xc1 // Set Baud rate 8-bit divisor Reg Address

#define RS232_BAUD_115200 ((16666666/115200/16)-1)// 8-bit divisor value to set

115200 baud

#define RS232_BAUD_57600 ((16666666/57600/16)-1) // 8-bit divisor value to set

57600 baud

#define RS232_BAUD_38400 ((16666666/38400/16)-1) // 8-bit divisor value to set

38400 baud

#define RS232_BAUD_19200 ((16666666/19200/16)-1) // 8-bit divisor value to set

19200 baud

#define RS232_BAUD_9600 ((16666666/9600/16)-1) // 8-bit divisor value to set

9600 baud

#define RS232_BAUD_4800 ((16666666/4800/16)-1) // 8-bit divisor value to set

4800 baud

Примечание, если KFLOP используется без Kanalog, выводы UART IO должны быть активированы, выполнив однократно следующую строку кода :

FPGA(KAN_TRIG_REG)=2;

Обратите внимание, что методы, показанные ниже, могут использоваться, но теперь доступен новый более простой и буферизованный метод. См. пример \C Programs\RS232\BufferedRS232.c

Пример передачи (RS232Send.c example)

#include "KMotionDef.h"

void SendChar(char c)

{

while (FPGA(RS232_STATUS) & RS232_TRANSMIT_FULL) ;

FPGA(RS232_DATA) = c;

}

main()

{

int i;

SetBitDirection(45,1);

FPGA(RS232_BAUD_REG) = RS232_BAUD_38400;

// FPGA(KAN_TRIG_REG) = 1; // enable Kanalog to get RS232

working

for (i=0;i<100;i++)

{

SendChar('A');

}

}

Пример приема (RS232Read.c example)

#include "KMotionDef.h"

void ReceiveChar()

{

// wait for data in buffer

while ((FPGA(RS232_STATUS) & 1)==0);

return FPGA(RS232_DATA);

}

main()

{

SetBitDirection(45,1);

FPGA(RS232_BAUD_REG) = RS232_BAUD_38400;

// FPGA(KAN_TRIG_REG) = 1; // enable Kanalog to get RS232

working

for (;;)

{

while ((FPGA(RS232_STATUS) &

RS232_DATA_READY) == 0) ;

printf("%X\n",ReceiveChar());

}

}