KFLOP/Kogna - RS232

RS232

KFLOP/Kogna contains a UART that can allow KFLOP/Kogna User C Programs to perform serial communication with other 3rd party devices.

KFLOP/Kogna itself contains the serial communication UART but does not have the circuitry to drive or receive the signals at the +3 to 25V to -3 to -25V voltages levels specified by the RS232 standard. The transmit and receive signals to/from KFLOP/Kogna are 3.3V LVTTL logic signals. Where a low logic level (<0.4V) represents the RS232 Space Level (>+3V) and a high logic level represents the RS232 Mark Level (< -3V).

Note that the signals that the signals coming directly from KFLOP/Kogna are not RS232 compatible. Connecting KFLOP/Kogna inputs directly to RS232 is likely to cause damage.

Some serial devices may be compatible with 3.3V logic. Also many 3rd party converters are available. A Internet search found this one (we haven't tested it).

http://www.commfront.com/TTL-RS232-RS485-Serial-Converters/RS232-TTL3.3V-Converter.htm

Our Kanalog board has a LVTTL to converter on board (see next section below).

KFLOP/Kogna + Kanalog - RS232

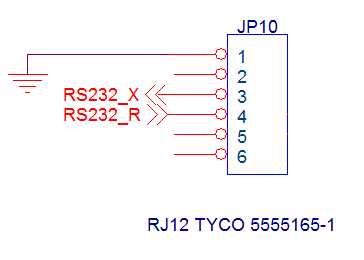

Kanalog contains circuitry to convert the KFLOP/Kogna UART logic levels to standard RS232 voltage levels. The RS232 signals are accessible from JP10 which is a standard RJ12 phone jack.

The pinout is shown below. The pinout is designed to be 1:1 compatible with certain PLC devices. Note that a phone cable with all 6 wires populated is required in order to make the pin 1 ground connection.

KFLOP/Kogna UART Software

The KFLOP/Kogna FPGA implements a programmable baud rate UART with double buffering of 1 character on transmit and receive. Currently a KFLOP/Kogna User C program must be used to make use of the UART. It is up to the User to program whatever is necessary to control any specific device.

KFLOP/Kogna User Programs with 1 active thread execute every 180us. (See here for more info). This allows rates up t0 38400 baud without loss if a character is read every time slice (10 bits at 38400Hz = 260us). Data transmitted and received is always 8 bits. If parity is required it should be handled by the User C program.

To set the baud rate write a defined 8-bit baud rate divisor to an FPGA Register (RS232_BAUD_REG )

To transmit a character an 8-bit character is written to an FPGA register (RS232_DATA).

To receive a character read an 8-bit value from an FPGA register (RS232_DATA )

A status register (RS232_STATUS) provides 2 bits of status that can be used to determine if a character has been received (RS232_DATA_READY) and if it is possible to transmit a character (RS232_TRANSMIT_FULL)

The following definitions have been added to the KMotionDef.h file.

//RS232 FPGA Register Definitions

#define RS232_STATUS 0xc1 // Status Reg Address

#define RS232_DATA 0xc0 // 8 bit data read/write reg address

#define RS232_DATA_READY 0x01 // Data ready to read status mask

#define RS232_TRANSMIT_FULL 0x02// Transmit buffer full status mask

#define RS232_BAUD_REG 0xc1 // Set Baud rate 8-bit divisor Reg Address

#define RS232_BAUD_115200 ((16666666/115200/16)-1)// 8-bit divisor value to set 115200 baud

#define RS232_BAUD_57600 ((16666666/57600/16)-1) // 8-bit divisor value to set 57600 baud

#define RS232_BAUD_38400 ((16666666/38400/16)-1) // 8-bit divisor value to set 38400 baud

#define RS232_BAUD_19200 ((16666666/19200/16)-1) // 8-bit divisor value to set 19200 baud

#define RS232_BAUD_9600 ((16666666/9600/16)-1) // 8-bit divisor value to set 9600 baud

#define RS232_BAUD_4800 ((16666666/4800/16)-1) // 8-bit divisor value to set 4800 baud

Note if KFLOP/Kogna is to be used without Kanalog the UART IO pins must be activated by executing the following line of code one time:

FPGA(KAN_TRIG_REG)=2;

Note: The techniques shown below may be used but a

new simpler and buffered method is now available.

See the \C Programs\RS232\BufferedRS232.c example.

Transmit Example (RS232Send.c example)

#include "KMotionDef.h"

void SendChar(char c)

{

while (FPGA(RS232_STATUS) & RS232_TRANSMIT_FULL);

FPGA(RS232_DATA) = c;

}

main()

{

int i;

SetBitDirection(45,1);

FPGA(RS232_BAUD_REG) = RS232_BAUD_38400;

// FPGA(KAN_TRIG_REG) = 1; // enable Kanalog to get RS232 working

for (i=0;i<100;i++)

{

SendChar('A');

}

}

Receive Example (RS232Read.c example)

#include "KMotionDef.h"

void ReceiveChar()

{

// wait for data in buffer

while ((FPGA(RS232_STATUS) & 1)==0);

return FPGA(RS232_DATA);

}

main()

{

SetBitDirection(45,1);

FPGA(RS232_BAUD_REG) = RS232_BAUD_38400;

// FPGA(KAN_TRIG_REG) = 1; // enable Kanalog to get RS232 working

for (;;)

{

while ((FPGA(RS232_STATUS) & RS232_DATA_READY) == 0) ;

printf("%X\n",ReceiveChar());

}

}